ПОСЛЕДОВАТЕЛЬНАЯ ЛОГИКА. ТРИГГЕРЫ

Вся рассмотренная в статье «Комбинационные логические схемы» цифровая логика строилась на комбинационных схемах (т. е. наборах вентилей), в которых выход полностью определяется текущим состоянием входов. В этих схемах отсутствует «память», отсутствует предыстория. Жизнь цифровой логики станет более интересной, если устройства снабдить памятью. Это дает возможность конструировать счетчики, арифметические регистры и различные «умные» схемы. Выполнив одну интересную функцию, они начинают делать другую. В последовательной логике выходы зависят также от состояния предыдущих выходов.

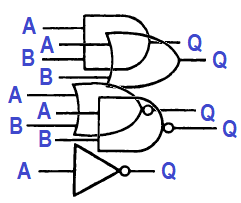

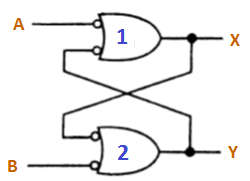

Основным узлом таких схем является триггер. Колоритное имя для описания устройств, которые в простейшей форме представлены на рисунке

Предположим, что оба входа А и В имеют высокий уровень. Тогда в каком состоянии будут выходы X и Y? Если X будет иметь высокий уровень, то последний будет присутствовать на обоих входах вентиля «2», и устанавливать Y в состояние низкого уровня. Это согласуется с состоянием выхода X (высокий уровень), следовательно, все правильно. Не правда ли?

X = Высокий, Y = Hизкий.

Неверно! Схема симметрична, следовательно, правомерно будет и состояние, при котором

X = Низкий, Y = Bысокий.

Состояние, когда оба выхода X и Y имеют высокий (или низкий) уровень, невозможно (А = В = Высокий уровень). Таким образом, триггер имеет два устойчивых состояния (иногда его называют «бистабильной» схемой). В каком из этих двух состояний он окажется, зависит от его предыстории, т. е. он обладает памятью. Для того чтобы в эту память что-то записать, достаточно на один из входов триггера кратковременно подать низкий уровень. Например, после кратковременной подачи низкого уровня на вход А триггер гарантированно установится в состояние

X = Высокий, Y=Hизкий

независимо от того, какое состояние он имел прежде.

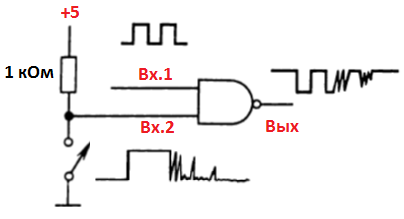

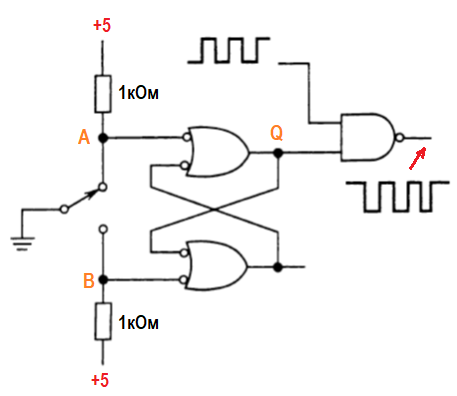

Подавление дребезга контактов. Рассмотренный нами триггер с входами S (установки в «1») и R (установки в «0» или сброса) оказывается весьма полезным для многих применений. На рисунке показан типичный пример его использования.

По идее эта схема должна открывать вентиль и пропускать входные импульсы, если ключ разомкнут. Ключ связан с землей (а не с шиной 4-5 В). Что характерно для биполярных ТТЛ-схем (в противоположность КМОП-элементам). Так как мы должны обеспечить отвод тока от входа ТТЛ в состоянии низкого уровня (0,25 мА для LSTTL), в то время как в состоянии высокого уровня входной ток близок к нулю. Кроме того, обычно в устройствах имеется шина земли, удобная для подсоединения к ней ключей и других органов управления.

При использовании такой схемы возникает проблема, обусловленная «дребезгом» контактов ключа. За время порядка 1 мс после замыкания ключа его контакты входят в соприкосновение друг с другом обычно от 10 до 100 раз. Вы получите в итоге форму сигналов, указанную на рисунке. Если бы выход подключался к счетчику или регистру сдвига, то они наверняка отреагировали бы на каждый дополнительный импульс дребезга контактов.

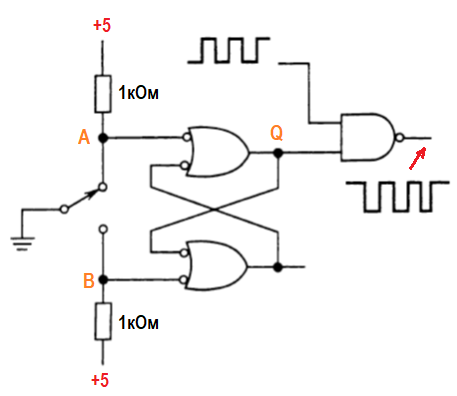

На рисунке ниже показано, как разрешить эту проблему.

При первом же соприкосновении контактов триггер изменит свое состояние. В дальнейшем уже не будет реагировать на последующий дребезг, поскольку двухпозиционный однополюсный ключ не может совершать колебания до противоположной позиции. В результате дребезг выходного сигнала будет отсутствовать, как и показано на диаграмме.

Такая схема подавления дребезга широко используется. Так, микросхема sn74ls279n имеет четыре SR-триггера в одном корпусе.

К сожалению, схема имеет небольшой недостаток. Дело в том, что первый импульс, возникающий на выходе вентиля после его открытия, может оказаться укороченным. Это можно определить по моменту, замыкания ключа по отношению к входной серии импульсов. То же самое относится и к конечному импульсу последовательности. В тех случаях, когда этот нежелательный эффект может оказать какое-то значение, применяется схема синхронизатора, которая позволяет его устранить.

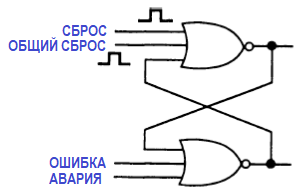

Многовходовые триггеры. На рисунке показана еще одна простая схема триггера.

В ней использованы вентили ИЛИ-HE: высокий уровень на входе устанавливает соответствующий выход триггера в состояние низкого уровня. Устанавливать или сбрасывать триггер различными сигналами можно благодаря наличию нескольких входов. На этом схемном фрагменте нагрузочные резисторы не используются. Входные сигналы формируются где-нибудь в другом месте (с помощью стандартных выходов с активной нагрузкой).

Тактируемые триггеры

Триггеры, выполненные на двух вентилях, как показано на рисунках выше, обычно называют RS (от английских слов: set- «установка» и reset-«сброс»), или асинхронными триггерами. Посредством подачи соответствующего входного сигнала они могут быть установлены в то или иное состояние. RS -триггеры удобно использовать в схемах защиты от дребезга и многих других случаях.

Однако более широкое применение получили триггеры, схема которых несколько отличается. Вместо пары асинхронных входов они имеют один или два информационных входа и один тактирующий вход. В момент подачи тактирующего импульса выходное состояние триггера либо изменяется, либо остается прежним, в зависимости от того, какие сигналы действуют по информационным входам.

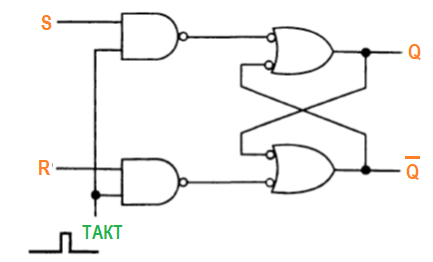

Простейшая схема тактируемого триггера приведена на рисунке ниже:

От рассмотренной выше схемы она отличается наличием двух вентилей («SET» и «RESET»). Легко проверить, что таблица истинности для этого триггера будет иметь вид

где Qn+1- состояние выхода Q после подачи (n+1)-го тактового импульса, a Qn — до его поступления. Главное отличие этой схемы от предыдущей состоит в том, что входы S и R в этом случае должны рассматриваться как информационные. Сигналы, присутствующие на этих входах в момент поступления тактового импульса, определяют, что произойдет с выходом Q.

У этого триггера есть один недостаток. Дело в том, что изменение выходного состояния в соответствии с входными сигналами может происходить в течение всего отрезка времени, на котором тактовый импульс имеет высокий уровень. В этом смысле он еще подобен асинхронному RS-триггеру.

Эта схема известна также под названием «прозрачный фиксатор». Назвали ее так потому, что выход «насквозь просматривает» вход в течение интервала действия тактового сигнала. Всесторонние возможности триггерных схем раскроются после введения новых, нескольких отличных от рассмотренных конфигураций. Новые конфигурации представляют собой триггер типа «ведущий-ведомый» (двухступенчатый) и триггер, запускаемый по фронту.

Триггеры типа «ведущий-ведомый» и триггеры, запускаемые по фронту.

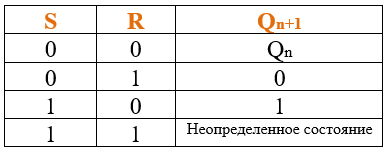

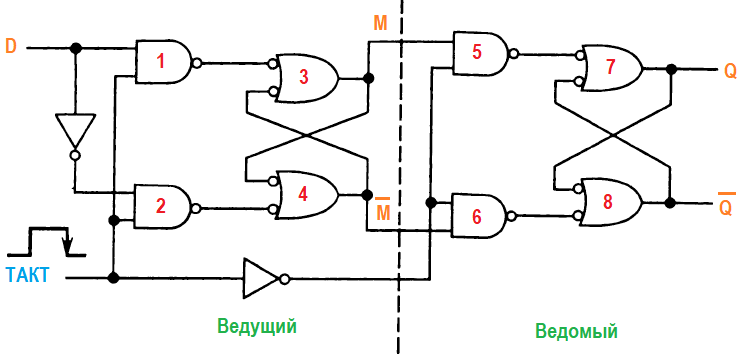

Эти типы триггеров наиболее распространены. Информация, поступившая на входные линии этого триггера к моменту возникновения перехода или «фронта» тактового сигнала, определяет, каким будет состояние выхода в последующий интервал времени. Такие триггеры выпускаются в виде недорогих интегральных микросхем. Для того чтобы понять, как они работают, имеет смысл рассмотреть их внутреннюю структуру. Рассмотрим принципиальные схемы так называемых D-триггеров.

Информация, поступившая на D-вход, передается на выход Q после подачи тактового импульса. Для начала принцип действия триггера типа ведущий-ведомый:

Если тактовый сигнал имеет высокий уровень, разрешается работа вентилей 1 и 2. Через эти вентили ведущий триггер (вентили 3 и 4) устанавливается в состояние, соответствующее D-входу: М = D, М’ = D’. Вентили 5 и 6 закрыты, поэтому ведомый триггер (вентили 7 и 8) сохраняет свое предыдущее состояние.

Когда тактовый сигнал перейдет в состояние низкого уровня, входы ведущего триггера отключатся от D-входа, а входы ведомого подключатся к выходу ведущего. В результате ведущий передаст свое состояние ведомому триггеру. После этого никакие изменения на выходе произойти не смогут, так как ведущий триггер заблокирован. С приходом следующего тактового сигнала ведомый триггер отключится от ведущего, а ведущий воспримет новое состояние входа.

С точки зрения внешних сигналов триггер, срабатывающий по фронту, ведет себя точно также, однако внутри он работает по-другому. Принцип его действия нетрудно разобрать самостоятельно. Схема, показанная на рисунке б, представляет собой распространенный D-триггер 74 семейства ТТЛ (пример).

Срабатывает он на положительном перепаде. В рассмотренном ранее триггере типа «ведущий-ведомый» данные на выход передавались по отрицательному перепаду тактового импульса. В интегральные микросхемы, выпускаемые промышленностью, входят триггеры, срабатывающие как по одной, так и по другой полярности перепада.

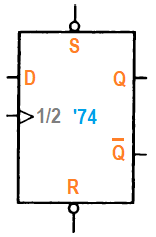

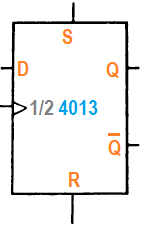

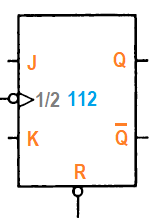

Кроме того, большинство триггеров имеют также асинхронные входы S и R. Они могут устанавливаться или сбрасываться как высоким, так и низким уровнем в зависимости от типа триггера. На рисунке ниже показано несколько популярных триггеров. Стрелка обозначает динамический вход (срабатывание по фронту), а кружок-инверсию.

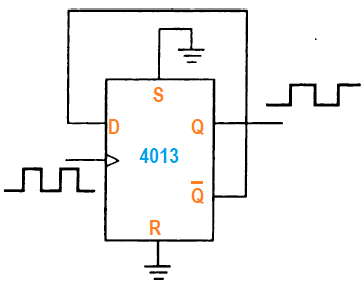

Таким образом, изображенная на рисунке схема микросхемы 74 семейства представляет собой сдвоенный D-триггер, который срабатывает по положительному перепаду и имеет асинхронные входы S и R, активные по низкому уровню.

Схема 4013 представляет собой сдвоенный D-триггер семейства КМОП, срабатывающий по положительному перепаду и имеющий асинхронные входы S и R, активные по высокому уровню.

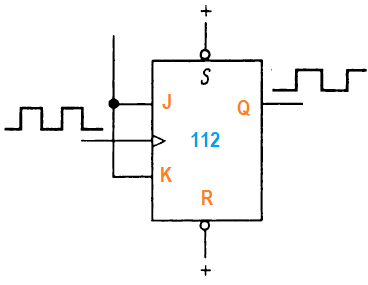

Интегральная схема 112 — это сдвоенный JK-триггер типа ведущий- ведомый, срабатывающий по отрицательному перепаду и имеющий асинхронные входы S и R, активные по низкому уровню.

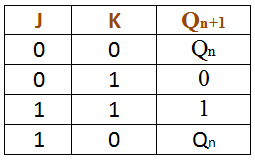

JK-триггер. По принципу действия JK-триггер аналогичен D-триггеру, но имеет два информационных входа. Его таблица истинности имеет вид:

Если на входы поступают противоположные сигналы, то на очередном фронте тактового импульса выход Q воспроизводит значение J-входа. Если оба входа J и К имеют низкий уровень, то состояние выхода не изменится. И наконец, если на обоих входах высокий уровень, триггер будет совершать «переброс». Менять свое состояние на каждом тактовом импульсе, т. е. работать в счетном режиме.

Предупреждение. Некоторые старые типы JК-триггеров представляют собой «ловушку для единиц». Этот термин вы не найдете ни в одной документации. Он означает явление, которое может привести неосведомленного человека к весьма неприятным последствиям. Дело в том, что если на интервале, когда ведомый триггер открыт тактовым сигналом, входы J или К (или оба одновременно) на какой-то момент изменят свое состояние, а затем до окончания тактового сигнала вернутся в исходное, то это кратковременное состояние триггер запомнит. И в дальнейшем он будет вести себя так, как если бы это состояние сохранилось.

В результате триггер может переброситься на следующем тактовом перепаде, даже если сигналы, действующие в момент этого перепада на входах J и К подтверждают предыдущее состояние. Это может привести, мягко говоря, к своеобразному поведению. Проблема возникает из-за того, что эти триггеры были сконструированы в предположении, что тактовый импульс имеет очень короткую длительность. В то время как в действительности тактирование всегда производится сигналом конечной длительности.

Если используется триггер типа «ведущий-ведомый», следует соблюдать меры предосторожности, либо вообще избегать их. При этом применяя более надежные триггеры, работающие по фронту. Две хорошие альтернативы, которые используют истинно запуск по фронту, это приборы 112 семейства (пример) и 109 семейства (пример). Оба представляют собой сдвоенные (два в одном корпусе) JК-триггеры с асинхронными S- и R-входами, активными по низкому уровню.

Устройство 112 срабатывает по отрицательному фронту тактового сигнала, а устройство 109-по положительному. Схема серии 109 имеет интересную особенность, а именно, К-вход у него инверсный, поэтому иногда его называют JK-триггер с запретом. Таким образом, если вы соедините входы J и К вместе, то получите D-триггер. Для перевода его в счетный режим вы заземляете вход К’, а на входе J устанавливаете ВЫСОКИЙ уровень.

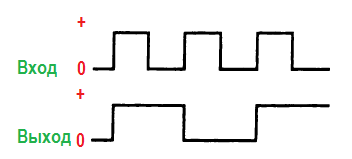

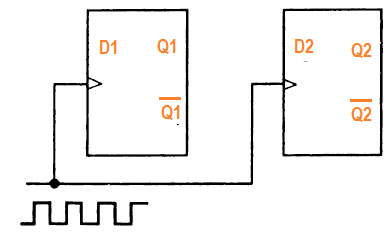

Делитель на 2. Легко построить схему делителя на 2, используя способность триггеров работать в счетном режиме. На рисунке показаны два способа построения такого делителя.

JK-триггер работает в счетном режиме, когда оба входа имеют ВЫСОКИЙ уровень, производя на выходе сигнал, показанный на рисунке. Вторая схема также будет совершать перебросы, так как ее D-вход подключен к собственному выходу Q. В момент поступления тактового импульса на D-входе всегда действует инверсия по отношению к текущему состоянию триггера. Частота сигнала на выходе в любом случае будет равна половине входной частоты.

Синхронизация информации и тактирование. В связи с последней схемой возникает интересный вопрос: не получится ли так, что триггер не сможет переброситься, так как состояние D-входа изменяется почти сразу же вслед за тактовым импульсом? Другими словами, не начнет ли схема сбиваться, если на ее входе происходят такие странные явления? Этот вопрос можно сформулировать по-другому: в какой точно момент по отношению к тактовому импульсу D-триггер (или какой-нибудь другой) анализирует состояние своего входа?

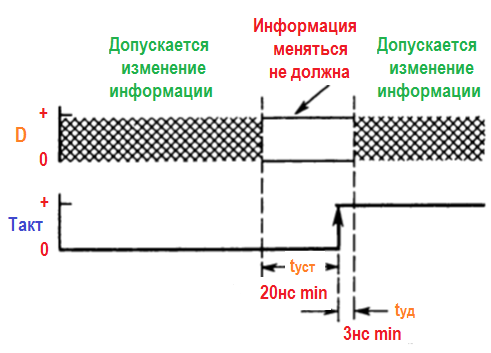

Ответ такой: для любого тактируемого устройства существует определенное «время установления» tуст и «время удержания» tуд. Для того чтобы схема работала правильно, информация должна поступать на вход не позднее чем за время tуст до возникновения тактового перепада и оставаться неизменной по крайней мере в течение времени tуд после него.

Например, для триггера 74НС74, tуст = 20 нс и tуд = 3 нс.

В рассмотренной схеме счетного триггера требование к времени установления будет сохраняться неизменным в течение как минимум 20 нс, предшествующих очередному тактовому перепаду. Может показаться, что при этом нарушается требование к времени удержания, но это не так. Минимальное время распространения сигнала с тактового входа на выход составляет 10 нс. D-триггер, включенный в счетном режиме, будет иметь неизменное состояние D-входа в течение по меньшей мере 10 нс.

Большинство современных устройств вообще не представляют требований ко времени удержания (имеют tуд = 0). Если сигнал на D-входе изменяется на интервале времени удержания, то может возникнуть любопытный эффект. Этот эффект носит название «метастабильное состояние». При нем триггер не может определить, в какое состояние он должен перейти.

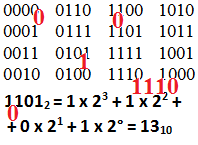

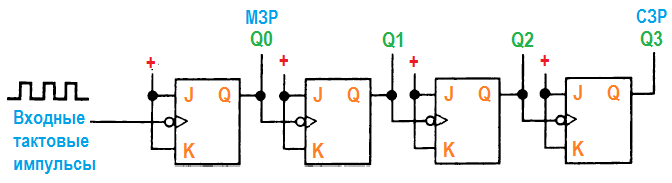

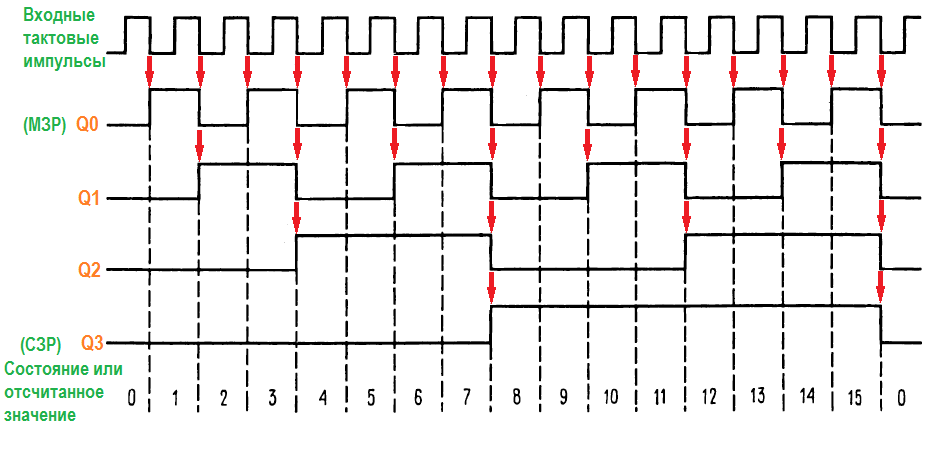

Деление на число, большее чем 2. С помощью каскадного соединения счетных триггеров легко получить «делитель на 2n», или двоичный счетчик. При этом выход Q каждого предыдущего триггера подключен к тактическому входу последующего. На рисунке ниже показана схема четырехразрядного асинхронного счетчика и даны его временные диаграммы.

Заметим здесь, что если выход Q каждого триггера непосредственно действует на тактовый вход следующего, срабатывание триггеров должно происходить по спаду (заднему фронту) сигнала на тактовом входе (показано кружком инверсии). Эта схема представляет собой счетчик-делитель на 16. На выходе последнего триггера формируются прямоугольные импульсы, следующие с частотой, равной 1/16 частоты входного тактового сигнала.

Схема называется счетчиком, поскольку информация, присутствующая на четырех входах Q, может рассматриваться как 4-разрядное двоичное число. Это число изменяется от 0 до 15, увеличиваясь на единицу с каждым входным импульсом. Этот факт отражает временная диаграмма на рисунке

Здесь СЗР означает «старший значащий разряд», МЗР — «младший значащий разряд», стрелки указывают, какими перепадами вызываются изменения сигналов.

Этот счетчик, на самом деле, выполняет очень важную функцию. Выпускается в виде большого числа модификаций на однокристальных микросхем. Включает такие форматы счета, как 4-разрядный, двоично-десятичный и многоцифровой. Соединяя эти счетчики каскадно и воспроизводя их содержимое с помощью цифрового индикатора (например, светодиодного), можно легко построить схему подсчета каких-либо событий.

Если разрешить прохождение импульсов на вход счетчика в течение ровно 1 с, то получится счетчик частоты. Счетчик будет воспроизводить значение частоты путем подсчета числа периодов в секунду. Промышленностью выпускаются однокристальные счетчики частоты, в состав которых входят дополнительно генератор, схемы управления и вывода на индикацию.

На практике простейшая схема каскадирования счетчиков посредством соединения каждого выхода Q со следующим тактовым входом имеет некоторые интересные проблемы. Эти проблемы связанны с покаскадной задержкой распространения сигнала по цепочке триггеров. По этой причине лучше использовать схему, в которой один и тот же тактовый сигнал подается одновременно на все входы.

Объединение памяти и вентилей

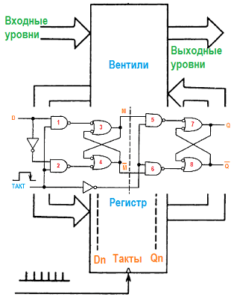

Посмотрим, что можно получить, если объединить триггеры с комбинационной (вентильной) логикой. Составленные из вентилей и триггеров схемы, представляют собой наиболее общую форму цифровой логики.

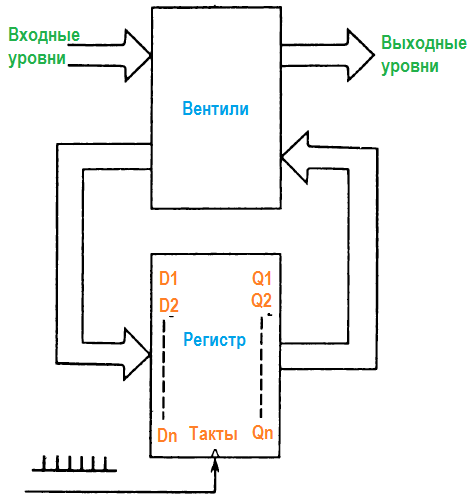

Синхронные тактируемые системы. Как говорилось выше, последовательные логические схемы, в которых для управления всеми триггерами используется общий источник тактовых импульсов, имеют ряд преимуществ. В таких синхронных системах все действия происходят сразу же после возникновения тактового импульса и определяются тем состоянием, которое имеет место непосредственно перед его возникновением. Общая структура подобной системы показана на рисунке.

Все триггеры объединены в один общий регистр, представляющий собой не что иное, как набор D-триггеров. У этих триггеров тактовые входы соединены вместе, а индивидуальные D-входы и выходы Q выведены вовне. Каждый тактовый импульс вызывает передачу уровней, присутствующих на D-входах, на соответствующие выходы Q. Блок, состоящий из вентилей, анализирует состояние выходов регистра и внешних входов, вырабатывает новую комбинацию сигнала для D-входов регистра и выходные логические уровни. Эта с виду простая схема обладает очень большими возможностями. Рассмотрим пример.

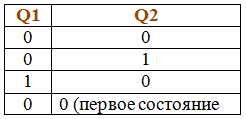

Пример: деление на 3. Попробуем построить схему синхронного делителя на 3 с помощью двух D-триггеров, тактируемых входным сигналом. В этом случае D1 и D2 будут входами регистра, Q1 и Q2 — его выходами, общая тактовая линия будет представлять главный тактовый вход:

1. Выберем три состояния:

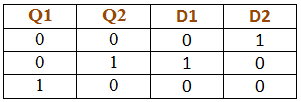

2. Определим, что должно поступать на D-входы, для того чтобы получить требуемые состояния на выходах:

- Построим вентильную схему, которая, с помощью имеющихся выходов, позволяла бы получить требуемые состояния на выходах. В общем случае можно использовать карту Карно, но для данного простого примера можно сразу увидеть, что

D1 = Q2, D2 = (Q2+Q2)’.

Этому соответствует следующая схема:

Легко проверить, что эта схема работает так, как и было задумано. Так как она является синхронной, или тактируемой, сигналы на обоих выходах изменяются одновременно. Если же выход первого триггера непосредственно подключить к тактовому входу второго, то получится асинхронный счетчик. В общем случае предпочитают использовать синхронные (или тактируемые) системы, так как они имеют более высокую помехоустойчивость. Это обусловлено тем, что к моменту возникновения тактового импульса триггеры находятся в установившемся состоянии. На схемы же, в которых входные сигналы анализируются только по фронтам тактовых импульсов, не действуют помехи. Помехи могут возникать за счет емкостных связей от других триггеров или по каким-либо другим причинам.

Еще одно преимущество состоит в том, что в тактируемых системах переходные состояния вызываются с задержками, в результате чего выходные сигналы изменяются не одновременно. И это не вызывает на выходах ложных сигналов, поскольку система не воспринимает никаких изменений, которые происходят после возникновения импульса.

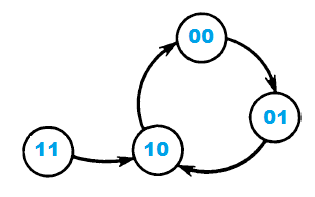

Запрещенные состояния. Что произойдет со схемой деления на 3, если ее триггеры каким-то образом окажутся в состоянии (Q1,Q2) = (1,1)? Это может произойти при включении питания, так как начальное состояние триггеров предсказать невозможно. Из схемы видно, что первый тактовый импульс переведет ее в состояние (1, 0) и далее она будет функционировать как положено. В таких случаях важно производить проверку запрещенных состояний. Ведь схема может случайно оказаться в одном из них. С другой стороны, все возможные состояния системы можно определить на начальном этапе разработки. Диаграмма состояний, показанная для данного примера на рисунке ниже может оказаться полезным диагностическим инструментом.

Если в системе используются и другие переменные, то обычно для каждого перехода рядом со стрелкой записываются условия. Стрелки могут идти в обоих направлениях, а также из одного состояния к нескольким другим.

Диаграмма состояний как инструмент проектирования. Диаграмма состояний может оказаться полезной при разработке последовательной логики. Особо это характерно для тех случаев, когда переходы из одного состояния в другое могут происходить различным путем. Для создания такой схемы, нужно сначала выбрать совокупность единственных состояний системы. Затем каждому из них присвоить собственное имя (т. е. двоичный адрес).

Здесь потребуется не менее п триггеров, где n-наименьшее целое, для которого 2n больше или равно числу различных состояний системы. Далее устанавливают правила переходов из одного состояния в другое. Другими словами, все возможные условия для входа в каждое состояние и выхода из него. Таким образом, задача построения последовательной логики свелась к задаче построения комбинационной логики. Ее всегда можно решить с помощью известных методов, например, карты Карно.

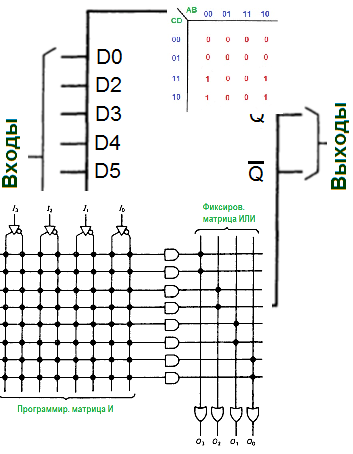

Регистровые ПЛМ. Программируемые логические интегральные микросхемы (ПМЛ и ПЛМ) выпускаются как с вентилями, так и с синхронно тактируемыми D-триггерами на одном кристалле. Они известны как регистровые ПМЛ и ПЛМ и являются идеальными для построения последовательных схем.

Синхронизатор

Интересно использование триггеров в последовательных схемах в качестве синхронизаторов. Предположим, что в синхронную тактированную систему с триггерами поступает внешний управляющий сигнал. Этот сигнал необходимо использовать для управления некоторым действием. Например, сигнал от измерительного прибора или экспериментальной установки может указывать, что данные готовы для передачи в ЭВМ. Экспериментальная установка и ЭВМ работают совершенно независимо друг от друга, т. е. асинхронно. И нам необходимо иметь метод, который позволил бы установить порядок в работе двух систем.

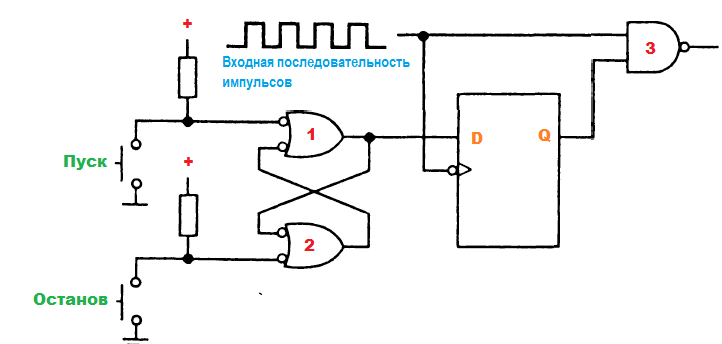

Пример: синхронизатор импульсов. Еще раз рассмотрим в качестве примера схему, в которой триггер подавителя дребезга разрешает прохождение последовательности импульсов

Эта схема открывает вентиль всякий раз, когда ключ замкнут, независимо от фазы, подаваемой на него импульсной последовательности. В результате первый или последний импульс могут оказаться укороченными. Задача состоит в том, что замыкание ключа происходит асинхронно с последовательностью импульсов. В некоторых случаях важно, чтобы все тактовые импульсы имели только полные периоды, и тогда нужно использовать схему синхронизации, подобную представленной ниже:

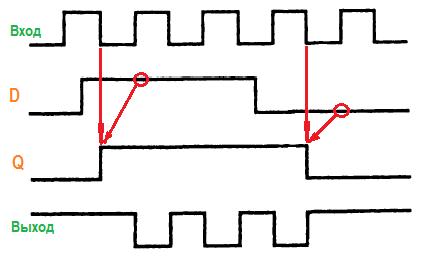

При нажатии кнопки «пуск» на выходе вентиля 1 возникает ВЫСОКИЙ уровень, но до появления заднего фронта очередного импульса на выходе Q триггера сохранится НИЗКИЙ уровень. В результате на выход вентиля 3 И-НЕ будут проходить только полные импульсы. На рисунке показаны временные диаграммы.

Стрелки показывают, какие действия вызываются соответствующими перепадами. Как видно из диаграммы, изменения Q происходят сразу по заднему фронту входного сигнала.

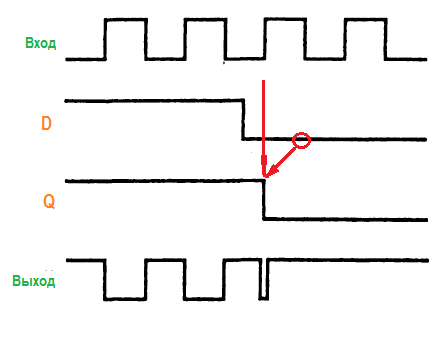

Логические состязания и «всплески». Рассмотренный пример позволяет осветить тонкий, но предельно важный вопрос: что же произойдет, если для переброса триггера будет использоваться положительный перепад? Если вы тщательно проанализируете этот случай, то увидите, что с ПУСКОМ схемы все будет в полном порядке, но если кнопку СТОП нажать в тот момент, когда на входе действует НИЗКИЙ уровень, произойдет весьма неприятная вещь.

Так как последний (3) вентиль И-НЕ будет открыт до тех пор, пока на выходе триггера не установится НИЗКИЙ уровень, на выходе схемы возникает короткий «выброс» или «всплеск» (глитч). Это-классический пример «логического состязания». Принимая определенные меры предосторожности, подобных ситуаций можно избежать, что и показывает рассмотренный пример. «Всплески» — это страшная вещь, если они заведутся в ваших схемах. Кроме всего прочего, их невозможно увидеть на осциллографе. Вы можете просто не узнать об их существовании. «Всплески» могут самым произвольным образом тактировать цепочки триггеров, они могут расширяться или сужаться до полного исчезновения, проходя через вентили и инверторы.

Замечаний по поводу синхронизаторов: На D-вход триггера сигнал может поступать не только от ключа с подавителем дребезга, но также и от других логических схем. В средствах сопряжения с ЭВМ и других применениях часто бывает нужно передавать асинхронный сигнал в тактируемое устройство. Идеальным решением в этих случаях является использование тактируемых триггеров или синхронизаторов.

В рассмотренной схеме, так же, как и во всех других логических схемах, необходимо соответствующим образом подключить неиспользованные входы. В данном случае входы S и R нужно подключить так, чтобы они не влияли на работу схемы. для микросхем 74 серии соединить с ВЫСОКИМ уровнем, а для 4013 заземлить. Неиспользуемые входы, не влияющие на выход (например, входы незадействованных вентилей), можно оставлять неподключенными. Это не относится к элементам КМОП, у которых они должны заземляться, чтобы не появился ток в выходном каскаде.