Проблемы логических схем. Недостатки ТТЛ и КМОП.

Существуют интересные, а иногда и просто забавные ловушки, подстерегающие ничего не подозревающего разработчика цифровых схем. Некоторые из них, такие как логические гонки и тупиковые ситуации, могут возникать независимо от типа используемых логических схем. Другие (как, например, эффект тиристорного включения в кристаллах КМОП) представляют собой «генетические аномалии» того или иного семейства. Ниже приводятся некоторые проблемы логических схем для предупреждения их в будущих проектах.

Проблемы статических режимов

«Тупиковое состояние». Легко попасть в ловушку, построив схему, имеющую «мертвое» состояние. Допустим, имеется какое-то устройство с рядом триггеров. Триггеры в процессе работы проходят через заданные состояния. Кажется, что схема действует превосходно, но в один прекрасный момент она намертво останавливается. Единственный способ заставить ее опять работать — выключить питание, затем снова его включить. Такая ситуация возникла из-за того, что схема имела «мертвое» состояние. Т.е. запрещенное состояние системы, которого не удалось избежать. Схема угодила в него под воздействием каких-то переходных помех по цепи питания.

При разработке цифровых схем очень важно выявить подобные состояния. Строить логику необходимо таким образом, чтобы схема могла автоматически восстанавливаться. Как минимум, должен быть предусмотрен сигнал начальной установки. Например, сигнал, вырабатываемый от кнопки, при включении питания. Этот сигнал мог бы возвращать систему в нормальное состояние. При наличии подобного сигнала никаких других мер может и не потребоваться.

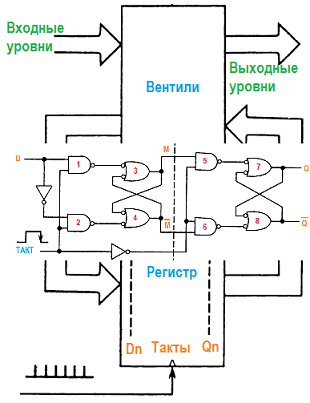

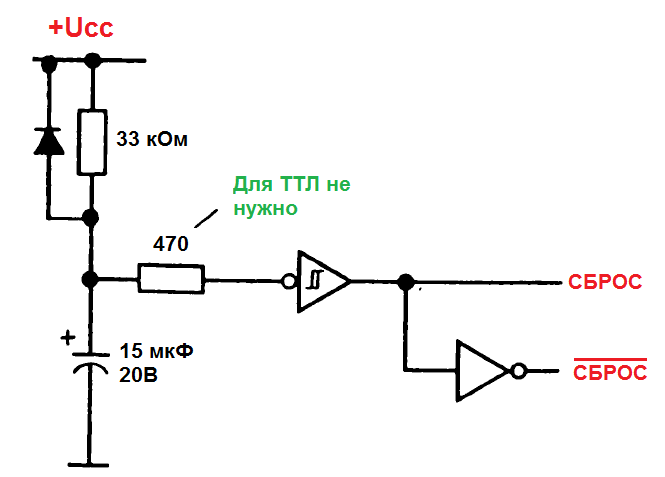

Начальная установка. Этот вопрос возникает при определении состояния системы в начальный момент. В любом случае полезно иметь какой-либо сигнал, который обеспечивал бы начальную установку. Иначе при включении питания в системе могут происходить непонятные вещи. На рисунке показана подходящая схема.

Последовательно включенный со входом вентиля резистор необходим при использовании КМОП-схем. Его использование позволяет избежать повреждения схемы при отключении питания. При отсутствии резистора электролитический конденсатор будет пытаться запитать систему через защитный диод входного вентиля КМОП.

Проблемы при переключениях

Логические гонки. Здесь скрываются многие коварные ловушки. Классический случай логических гонок был описан в разделе «Синхронизатор» на примере синхронизатора импульсов. В любом случае, когда вентили управляются сигналами от триггеров, необходимо убедиться в том, что в схеме не может возникнуть следующая ситуация. К моменту тактирования триггера вентиль открывается, а по истечении задержки на триггере закрывается. Сигналы, возникающие на входах триггеров, не должны быть задержанными по отношению к тактовым импульсам. (Еще одно преимущество синхронной системы!). В общем случае задерживайте такты, но не информацию. Необычно легко проглядеть возможность возникновения логических гонок.

Метастабильные состояния. Как уже отмечалось в разделе «Синхронизация информации и тактирование», триггер и любое тактируемое устройство могут сбиться, если изменение сигналов на информационных входах произойдет менее чем за время tycт до возникновения тактового импульса. В худшем случае выход триггера будет буквально совершать колебания в окрестности логического порога в течение нескольких микросекунд.

Для сравнения: нормальная величина задержки распространения элементов ТТЛ составляет 20 нс. Разработчики логических схем это обычно не принимают во внимание. Подобная проблема логических схем может возникнуть в быстродействующих системах, когда потребуется синхронизовать асинхронные сигналы. Такую ситуацию считают виновной во многих таинственных сбоях ЭВМ. В этом случае требуется лишь установить цепочку синхронизаторов или «детектор метастабильных состояний», который будет сбрасывать триггер.

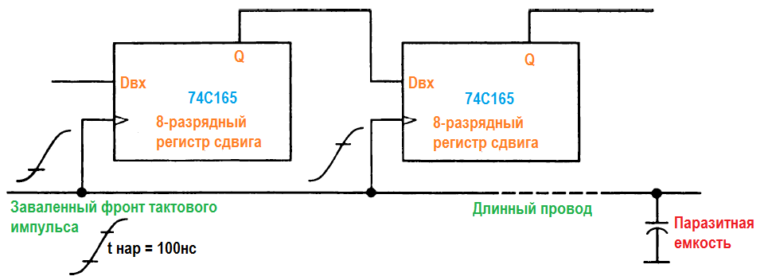

Скос фронтов тактовых импульсов. Скос фронтов тактовых импульсов оказывает большее влияние на схемы КМОП, чем на ТТЛ. Такая проблема возникает в том случае, когда для тактирования нескольких соединенных между собой устройств используется сигнал с большим временем нарастания:

В рассматриваемом примере два регистра сдвига тактируются фронтом с большим временем нарастания. Это время обусловлено емкостной нагрузкой выхода КМОП, который имеет относительно высокий импеданс. (Порядка 500 Ом при работе от источника 4-5 В). Проблема возникает из-за того, что порог срабатывания у первого регистра может оказаться ниже, чем у второго. В результате у первого регистра сдвиг произойдет раньше и последний бит первого регистра будет потерян.

Дело еще осложняется тем, что значения пороговых напряжений для устройств на КМОП колеблются в очень широком диапазоне. Фактически они могут принимать любое значение в пределах от 1/3 до 2/3 Ucc. В подобной ситуации самое лучшее располагать корпуса микросхем рядом. Это поможет избежать большой емкостной нагрузки по тактовым входам.

Говоря в общем, тактовые входы каких-либо цифровых микросхем должны всегда тщательно обрабатываться. Например, тактовые линии с шумом или «звоном» должны всегда очищаться с помощью вентиля (возможно, с входным гистерезисом) до подачи на синхронизируемый кристалл. Возможно появление проблемы с линиями синхронизации, которые поступают с другой платы или с другого логического семейства. Например, медленная логика 4000B или 74С, питающая быстрые семейства НС или АС, наверняка вызовет проблемы перекоса импульсов или кратных переходов.

Укороченные импульсы. Когда счетчики по модулю n должны сбрасываться собственным входным сигналом, необходимо ввести задержку для того, чтобы предотвратить появление укороченного импульса. Это же относится и к импульсам записи в счетчики или регистры сдвига. Укороченные импульсы часто доставляют неприятности, приводят схему к работе на границе устойчивости и вызывают периодические сбои. При разработке схемы следует исходить из наихудшего значения для задержки.

Неопределенные правила. Когда полупроводниковая промышленность нащупывала свой путь, было недопонято значение стандартизации выводов, спецификаций и функциональности. Как пример, схема 7400 (И-НЕ) имела свои выводы вентилей, а схема 7401 (ИЛИ-HE с открытым коллектором) имела отличные от нее расположения выводов вентилей. Это создавало такую путаницу, что побудило выпустить «мутант»-схему 7403, которая представляет собой схему 7401, но с разводкой вентилей, как у 7400.

Подобное недоразумение случилось со схемой 7490 (двоично-десятичный счетчик) с расположением контактов питания посередине корпуса, а не в углах.

Контакты питания, расположенные посредине корпуса, «возвратились» в быстродействующих схемах КМОП, для уменьшения индуктивности и улучшения изоляции.

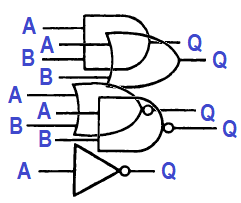

Важным наследством этой ранней анархии является «всякая всячина» неопределенных правил, которых мы придерживаемся. Например, популярный ’74 D-триггер существует в каждом логическом семействе. Подача одновременно сигналов установки и сброса приводит к высокому уровню на обоих выходах в каждом семействе. Кроме 74С, здесь это приводит к низкому уровню на выходах!

Это не совсем неопределенное правило. Если внимательно посмотреть в хорошую документацию, то найдется непоследовательность. На техническом жаргоне это называют «Попался!» (gotcha).

Другим примером этого «попался!» является схема ’96 — 5-разрядный сдвиговый регистр с хитрыми входами загрузки. Они могут устанавливаться, но не сбрасываться. Подлинным неопределенным правилом, а фактически очень важным является «время перемены». Это такое количество времени, которое необходимо ожидать после снятия асинхронного входного сигнала для полной гарантии синхронизации тактируемого элемента.

Проектировщиков кристаллов не беспокоило это обстоятельство, пока ранее выпускавшиеся логические семейства не были обойдены улучшенными ТТЛШ и быстрыми КМОП-семействами. Если вы проектируете с применением более ранней логики (например, 74С), предполагайте, что время перемены такое же, как время установки данных, хотя обычно оно меньше. Так, например, у D-триггера 74НС74 минимальное время распространения определяется в 5 нс, в то время как минимальное время установки данных составляет 20 нс.

Проблемы, причиняющие неудобства

Биполярные ТТЛ-элементы. Не следует забывать, что при низком уровне входы ТТЛ действуют как источник тока (например, 0,25 мА для LS, 0,5 мА для F). Это затрудняет использование RC-цепочек в качестве элементов задержки и подобных элементов. Все потому, что они в этом случае должны иметь низкое сопротивление. И необходимо серьезно подумать, когда мы сопрягаем сигналы линейных устройств с ТТЛ-входами.

Значение порога у элементов ТТЛ (и серий, которые их имитируют — НСТ и ACT) близко к уровню земли. Вследствие чего все это логическое семейство в известной степени подвержено влиянию помех. Так как эти логические семейства являются быстродействующими, они воспринимают короткие всплески по шине земли. Такие всплески часто возникают при быстрой смене состояний на выходах, что еще более осложняет проблему.

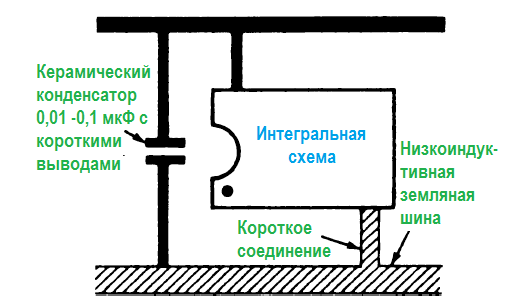

Биполярные ТТЛ-элементы предъявляют высокие требования к источнику высокой мощности рассеяния. Наличие токовых всплесков в шинах питания, которые вырабатываются схемами с активной нагрузкой, как правило, требует шунтирования источника питания. В идеальном случае — один конденсатор емкостью 0,1 мкФ на каждый корпус интегральной микросхемы.

КМОП-элементы. Выходы КМОП-элементов подвержены пробою под действием статического электричества. «Смертность» у КМОП действительно подскакивает в зимнее время! Семейства с поликремниевыми затворами [НС(Т), АС(Т)] значительно больше страдают, чем их предки с металлическими затворами. Входы КМОП имеют очень большой разброс по значениям порогового уровня. В сочетании с высоким выходным импедансом (200-500 Ом) это приводит к возникновению проблемы скоса фронтов тактовых импульсов. Когда на входе сигнал медленно нарастает, могут возникать двойные переключения на выходах. В устройствах на КМОП все неиспользованные входы, включая входы незадействованных вентилей, должны быть обязательно соединены с шиной высокого или низкого уровня.

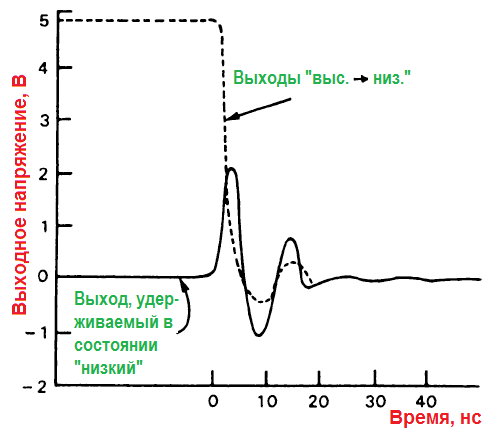

Интересная врожденная проблема быстродействующих КМОП-семейств в особенности АС и ACT состоит в наличии «подскока» уровня земли. Быстродействующий КМОП-элемент, работающий на емкостную нагрузку, генерирует громадные кратковременные токи по шине земли. Это приводит к тому, что потенциал на линии земли, подходящий к корпусу микросхемы, моментально подпрыгивает! В результате этого подпрыгивает и низкий уровень на выходах на том же самом кристалле. На рисунке ниже показан этот случай.

В особенности заметьте, что амплитуда этого эффекта от 1 до 2 В не является редкостью.

Давайте рассмотрим случай, когда время переключения составляет 3 нс, а перепад в 5 В прикладывается к емкости 50 пФ. В результате получаем мгновенное значение тока

I = CdU/dt = 83 мА

Так как 8-разрядный буфер может нагружаться непосредственно на такие же восемь нагрузок (при общем токе 2/3 А!), такое поведение схемы не является неожиданным. Эта задача приводит к спорному новому набору АС/АСТ-схем с «центральным» расположением выводов питания и земли (для снижения индуктивности).

Пользователи должны сознавать серьезность этой проблемы и принять меры для сохранения индуктивности шины земли на низком уровне, насколько это возможно, когда используется семейство АС/АСТ. Самым лучшим является использование печатных плат с распределенной шиной земли и множеством шунтирующих низкоиндуктивных конденсаторов. Лучший способ, если вам не нужна высокая скорость переключения, отказаться от семейства АС/АСТ, а использовать взамен серию НС/НСТ.

Аномальное поведение

Элементы ТТЛ. С элементами ТТЛ не связано такое большое число таинственных явлений, как с КМОП. Однако некоторые одновибраторы ТТЛ срабатывают от «глитчей» в цепи питания (или земли). Вообще, как правило, ведут себя в известной степени «нервно». Кроме того, схема, которая прекрасно работает на LS ТТЛ, может давать сбои, когда заменяется AS ТТЛ. Все из-за более быстрого переключения и увеличения токов потребления по цепям земли и окружению. В большинстве случаев неправильную работу ТТЛ-элементов можно связать с проблемой помех.

Элементы КМОП. КМОП-элементы способны свести с ума кого угодно! Например, схема может войти в режим «тиристорного защелкивания», если сигнал на входе (или выходе) возникает сразу после включения питания. Результирующий ток (50 мА или более) через диоды входной защиты включит пару паразитных перекрестно связанных транзисторов, которые являются побочным эффектом КМОП-технологии с изолированными переходами. При этом напряжение питания 17сс закорачивается на землю, кристалл начинает греться. Для того, чтобы схема снова начала правильно работать, потребуется отключить питание. Если это не сделать в течении нескольких секунд, то придется заменить микросхему.

Некоторые из КМОП-схем (серия НС с поликремниевыми затворами) невосприимчивы к «защелкиванию» даже с входным размахом 5 В выше уровня питания. Работают при входном размахе 1,5 В выше уровня питания.

Схема КМОП имеет весьма коварные и странные режимы ложной работы. Один из выходных полевых транзисторов может открыться, что приводит к кодозависимым ложным срабатываниям, которые очень трудно обнаружить. Вход может начать работать как источник тока или токовая нагрузка. Весь корпус может начать потреблять от источника питания существенный ток. Чтобы легче было обнаружить неисправную микросхему, потребляющую большой ток в статическом режиме, рекомендуется последовательно с контактом Ucc каждой микросхемы включить резистор 10 Ом. Для микросхем, нагруженных на большое число входов, или мощные драйверы, такие, как в серии АС, используйте резистор 1 Ом.

Кроме того, кристаллы КМОП дают большой разброс по входному порогу. При этом один и тот же кристалл может иметь неодинаковые значения порогового уровня для различных функций, выполняемых по одному и тому же входу.

Так, например, в устройстве CD4013 выход Q’ при управлении по R-входу переходит в состояние высокого уровня раньше, чем выход Q устанавливается в состояние низкого уровня. А это значит, что сигнал установки нельзя обрывать по изменению Q’, поскольку возникающий в этом случае импульс может не сбросить триггер.

Нельзя оставлять входы корпуса КМОП неподключенными. В этом случае схема время от времени может вести себя неправильно. Для того чтобы выявить неисправность, мы ставим щуп осциллографа в какую-то точку схемы. Обнаруживаем там уровень 0 В, как и должно быть. После этого в течение нескольких минут схема работает прекрасно, а затем снова сбивается! А произошло вот что: осциллограф разрядил неподключенный вход. Потребовалось достаточно большое время, чтобы он смог снова зарядиться до порогового уровня.

Дальше идет уже чистая фантастика. Вы забыли подключить контактный вывод Ucc корпуса КМОП, но все-таки схема просто идеально работает! А дело все в том, что она получает питание по одному из своих логических входов. От входа через защитный диод к цепи Ucc корпуса. Можно не замечать этого в течение довольно длительного времени. Пока не возникает ситуация, когда одновременно на всех входах корпуса будет действовать низкий уровень. Кристалл потеряет питание и «забудет» свое состояние.

В любом случае такой режим не может считаться нормальным. Выходной каскад не запитан нужным образом и не в состоянии обеспечить номинальный ток. Сложность состоит в том, что подобная ситуация может давать о себе знать лишь эпизодически. Порой приходится пробежать не один круг, пока, наконец, понимаешь, что же в действительности происходит.